製品情報

ZDAQ-Analog

- ZDAQ-Analog

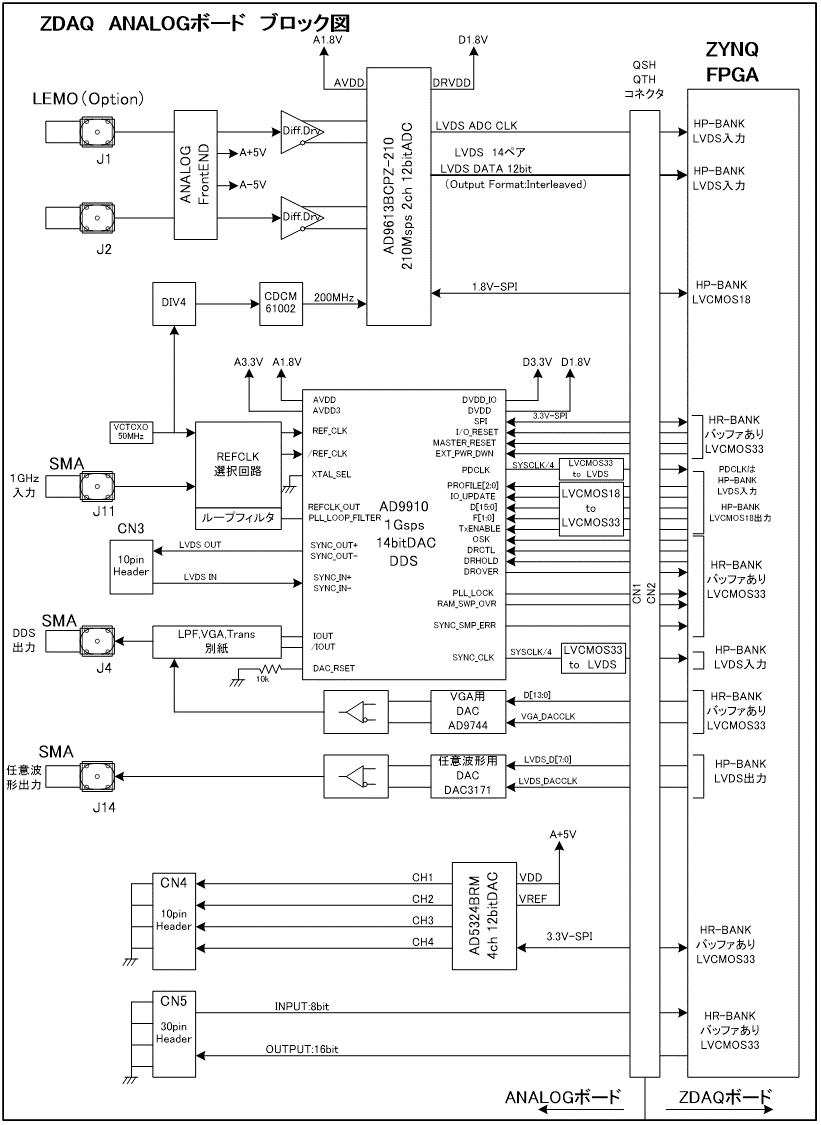

本製品は、1Gsps、14bitDAC を内蔵したダイレクト・ デジタル・シンセサイザAD9910を搭載しており、周波数シンセサイザや、プログラマブル・クロック・ジェネレータとして使用可能です。また、分解能12bit、サンプリング速度200MHzの高速ADCを2chと、分解能12bitのシリアルDAC も4ch搭載しています。

本製品は、ZDAQ-SoCの拡張コネクタに接続して使用するZDAQ-SoCのドータボードで、ZDAQ-SoC上のFPGAにより制御されます。CPU-

- 製品イメージ

- 仕様

- ドキュメント

- ブロック図

入出力 項目 仕様・機能 アナログ入力 入力チャネル数 2ch 入力レンジ ±5V(max) 入力形式 シングルエンド、 入力インピーダンス:50Ω コネクタ LEMO (実装option) ADC ADCタイプ PipeLineADC AD9613BCPZ 分解能 12bit、2.442mV/LSB サンプリング周波数 200MHz 出力モード LVDS-DDRモード アナログ出力 SPI-DAC AD5324BRM 分解能 12bit、1.221mV/LSB、Vref=5V 出力チャネル数 4ch 出力レンジ 0~5V コネクタ 10pinヘッダコネクタ DDS DDS AD9910 1Gsps、14bitDAC 正弦波出力 出力周波数 10~300MHz

下限はADL5330の特性による制限、上限はトランスによる制限出力可能周波数 5~400MHz

下限はチューニング目標、上限はサンプリング周波数による制限周波数分解能 0.23Hz (AD9910の仕様による) 出力波形 Acos(ωt+θ)

A,ω,θはAD9910 の仕様により設定可能。

ただし、ω=2π(FTW/2^32)fsysclk。

自動リニアまたは任意の周波数、位相、振幅スイープ機能出力形式 正弦波(AM波、FM波、PM波) AD9910の仕様による 出力電力 18dBm~-40dBm ADL5330およびAD9744を使用 出力電力分解能 14bit 0.004dB 掃引・変更 周波数の掃引・変更 AD9910の掃引・変更機能を使用可

またはソフトウエアでの単一周波数を更新する方法。内部クロック 周波数 VCTCXO-50MHz 周波数変動 温度ドリフト ±1ppm 20年間変動 ±3ppm 外部クロック 周波数 1GHz 周波数変動 周波数安定度 外部クロック精度による 入力レベル -3dBm~4dBm 入力Z:50Ω、コネクタ:SMA 温度ドリフト 外部信号源仕様による 年間変動 外部信号源仕様による 位相雑音 位相雑音 -105dBc/Hz @10KHz offset

-120dBc/Hz @100KHz offsetスプリアス 45dBc 任意波形出力 出力波形 三角波、鋸波、パルスなど

例:FPGAのRAMに書いたパターンデータを再生するパターン繰り返し周期 M/200Msps

Mは1サイクルのパターン再生に要するクロック数出力電圧 4Vp-p 最大 負荷抵抗1KΩ時

2Vp-p 最大 負荷抵抗50Ω時出力電圧分解能 出力電圧/14bit DAC型番 DAC3171 サンプリング周波数200MHz 電源 電圧 6V±10%、 消費電流:typ 1.4A ボードサイズ 200×150mm コネクタ突起部は含みません。 動作環境 真空中の動作可能 動作温度 0~50℃ パンフレット SP2814003-ZDAQ_Analog.pdf ハードウェア仕様書 ZDAQ-ANALOG-1_ハードウエア仕様書_Rev0p1_20170629.pdf